OBJETIVO

Comprobar y comprender el funcionamiento de las compuertas lógicas, así como el diseño de circuitos lógicos utilizando las mismas.

MARCO TEÓRICO

La figura representa un circuito multiplicador que toma dos números de 2 bits, X1X0 y Y1Y0 y produce un número binario de salida Z3Z2Z1Z0 que es igual al producto aritmético de los dos números de entrada. Diseñe el circuito lógico para el multiplicador utilizando el menor número posible de compuertas lógicas.Se tiene como marco teórico el uso de las tablas de verdad donde se muestra en una tabla la interacción de entradas y salidas en un circuito eléctrico. Donde se representan 1 y 0 para representar el estado de las variables booleanas que interactuan en el circuito. Así como las leyes de Morgan, propiedades y álgebra de Boole.

Mapas/Metodo de Karnaugh

Los Mapas de Karnaugh son una herramienta muy utilizada para la simplificación de circuitos lógicos. Cuando se tiene una función lógica con su tabla de verdad y se desea implementar esa función de la manera más económica posible se utiliza este método.

Ejemplo: Se tiene la siguiente tabla de verdad para tres variables:

Se desarrolla la función lógica basada en ella. (Primera forma canónica). Ver que en la fórmula se incluyen solamente las variables (A, B, C) cuando F cuando es igual a "1". Si A en la tabla de verdad es "0" se pone A, si B = "1" se pone B, Si C = "0" se pone C, etc.

F = A B C + A B C + A BC + A B C + A B C + A B C. Una vez obtenida la función lógica, se implementa el mapa de Karnaugh. Este mapa tiene 8 casillas que corresponden a 2n, donde n = 3 (número de variables (A, B, C)). La primera fila corresponde a A = 0La segunda fila corresponde a A = 1; La primera columna corresponde a BC = 00 (B=0 y C=0); La segunda columna corresponde a BC = 01 (B=0 y C=1); La tercera columna corresponde a BC = 11 (B=1 y C=1); La cuarta columna corresponde a BC = 10 (B=1 y C=0).

En el mapa de Karnaugh se han puesto "1" en las casillas que corresponden a los valores de F = "1" en la tabla de verdad. Tomar en cuenta la numeración de las filas de la tabla de verdad y la numeración de las casillas en el mapa de Karnaugh. Para proceder con la simplificación, se crean grupos de unos que tengan 1, 2, 4, 8, 16, etc. (sólo potencias de 2). Los unos deben estar adyacentes (no en diagonal) y mientras más unos tenga el grupo, mejor. La función mejor simplificada es aquella que tiene el menor número de grupos con el mayor número de unos en cada grupo

Se ve del gráfico que hay dos grupos cada uno de cuatro unos, (se permite compartir casillas entre los grupos).

La nueva expresión de la función boolena simplificada se deduce del mapa de Karnaugh.

- Para el primer grupo (rojo): la simplificación da B (los uno de la tercera y cuarta columna) corresponden a B sin negar)

- Para el segundo grupo (azul): la simplificación da A (losunos están en la fila inferior que corresponde a A sin negar)

Entonces el resultado es F = B + A ó F = A + B

Ejemplo: Una tabla de verdad como la de la derecha da la siguiente función booleana: F = ABC + AB C + A B C + A B C

Se ve claramente que la función es un reflejo del contenido de la tabla de verdad cuando F = "1". Con esta ecuación se crea el mapa de Karnaugh y se escogen los grupos. Se lograron hacer 3 grupos de dos "1"s cada uno.

Se puede ver que no es posible hacer grupos de 3, porque 3 no es potencia de 2. Se observa que hay una casilla que es compartida por los tres grupos.

La función simplificada es: F = AB + A C + B C (Grupo en azul: AB, grupo marrón: AC, grupo verde: BC)

Álgebra de Boole

1. Definición. El álgebra booleana es un sistema algebraico definido en un conjunto B, el cual contiene dos o más elementos y entre los cuales se definen dos operaciones denominadas "suma u operación OR" ( + ) y "producto o multiplicación u operación AND" ( ), las cuales cumplen con las siguientes propiedades:

2. Existencia de Neutros. Existen en B el elemento neutro de la suma, denominado O y el neutro de la multiplicación, denominado 1, tales que para cualquier elemento x de s: (a) x + O = x (b) x. 1 = x

3. Conmutatividad. Para cada x, y en B: (a) x+y = y+x (b) x y =y x

4. Asociatividad. Para cada x, y, z en B: (a) x + (y + z) = (x + y) + z (b) x (y z) = (x y) z

5. Distributividad. Para cada x, y, z en B: (a) x+(y z)=(x+y) (x+z) (b) x (y+z)=(x y)+(x z)

6. Existencia de Complementos. Para cada x en B existe un elemento único denotado x (también denotado x’), llamado complemento de x tal que (a) x+x = 1 (b) x = O.

Leyes de Morgan

1. El producto lógico negado de varias variables lógicas es igual a la suma lógica de cada una de dichas variables negadas. Si tomamos un ejemplo para 3 variables tendríamos:

~ (a.b.c) = ~a + ~b + ~c

2. La suma lógica negada de varias variables lógicas es igual al producto de cada una de dichas variables negadas:

~ (a + b + c) = ~a . ~b . ~c

DESARROLLO

En este apartado se explica el desarrollo del proyecto, así como los cambios que el mismo sufrió durante el proceso. Como primer paso tenemos la realización de las tablas de verdad; las cuales se hacen tomando los valores que tendrán las entradas siendo 1 o 0; para tener pues salidas que serán también pues 1 o 0.

Así pues, podemos diseñar la siguiente tabla de verdad, donde se nombra A, B el primer número binario; mientras que C, D es el segundo número binario. La salida seá S3, S2, S1, S0; es decir un número binario de 4 bits representados por 4 leds que indicaran si es 1 o 0.

Como vemos en la tabla se tienen varios resultados que al final serán mostrados como un conjunto de LED que indican el valor del bit que ocupa. Posteriormente se divide cada salida con el mismo conjunto de entradas para así hacer una tabla de verdad de cada número.

Utilizando el método de Karnugh para cada salida obtendremos las siguientes tablas:

Posteriormente ordenando los términos de cada mapa de Karnaugh, obtendremos una función para cada LED, que representara cada bit.

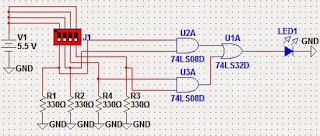

Para el bit 0 se obtiene que su función es ; quedando el diagrama de conexión; así:

Para el bit 2 la función es , con la siguiente conexión:

Y para el bit 3 la función es con el siguiente diagrama de conexión:

Después de varias consideraciones y conexiones erróneas se decidido por cambiar las resistencias de valor, de 330 Ω a 1500 Ω. Se hizo un circuito donde simplemente se empalmaba cada función para cada bit, el cual quedo de la siguiente manera:

En este podemos notar el excesivo uso de compuertas lógicas, siendo 6 NOT (74LS04), 15 AND (74LS08) y 5 OR (74LS32); con un total de 26 de ellas. Se hizo una agrupación de términos comunes de multiplicación (BC, BD, AD, AC) y la suma (C'+B',A'+D',B'+D') (el apostrofe indica negación). Quedando el circuito:

En este circuito se utilizan 4 NOT (74LS04), 8 AND (74LS08) y 4 OR (74LS32); siendo 16 compuertas lógicas.

Después de revisar los apuntes y comprobar que el circuito aun se puede simplificar más mediante la ley de Morgan que nos dice . Por lo que podemos cambiar los términos de suma que previamente se tenía por la negación de su multiplicación. Siendo las fórmulas para cada salida . Rehaciendo el circuito:

Donde se puede constatar que se utilizan 2 NOT (74LS04), 7 AND (74LS08) y 1 OR (74LS32); dando un total de 10 compuertas lógicas.

Posteriormente se paso a considerar el diseño, dándose cuenta la salida 2 es una suma exclusiva (74LS86) entre AD y BC, haciendo el cambio:

En este último circuito se tienen 1 NOT (74LS04), 6 AND (74LS08) y 1 XOR (74LS86); dando un total de 9 compuertas lógicas. 9 compuertas lógicas parece un pequeño número después del primer diseño de 26 compuertas lógicas.

Siendo que los circuitos integrados 74LS08, 74LS32 Y 74LS86 traen 4 de compuertas AND, OR y XOR respectivamente se usaría 2 74LS08, 1 74LS04 y 1 74LS86; siendo un total de 4 circuitos integrados. Tanto en la simulación como el circuito se nota que se dio un color a cada entrada, siendo café A, azul B, verde C y amarillo D; para contar con mayor orden. En el circuito físico se tienen las salidas y conexiones intermedias con gris, mientras que la alimentación y tierra de los integrados en negro. Haciendo un circuito esquemático:

Siendo el circuito a armar el siguiente.

Este circuito fue implementado en la tablilla de experimentación, siguiendo el esquema de colores previamente implementado, usando como tierra de conexiones sin utilizar el naranja.

Se armo el circuito 2 veces con 2 diferentes errores, el primero fue conectar todas las salidas no utilizables a tierra causando un cortocircuito y un calentamiento del CI 74LS04, el siguiente error que nos causaba variación en los resultados fue la no conexión a tierra del primer integrado 74LS08, causando errores al operar 2*3, 3*3, 3*2; siendo S0 la única que causaba problemas; al resolver este problema instantáneamente todas las operaciones fueron con los resultados correctos.

No hay comentarios:

Publicar un comentario